SiP係統級封裝錫膏焊料深圳福英達分享:集成的尺度和維度

SiP係統級封裝錫膏焊料深圳福英達分享:集成的尺度和維度

錫膏_焊錫膏_超微焊料_助焊膏生產(chan) 商-深圳福英達是一家集錫膏、錫膠及合金焊粉產(chan) 、銷、研與(yu) 服務於(yu) 一體(ti) 的綜合型錫膏供應商, 是工信部焊錫粉標準製定主導單位,產(chan) 品涵蓋超微無鉛印刷錫膏,超微無鉛點膠錫膏,超微無鉛噴印錫膏,超微無鉛針轉移錫膏,超微無鉛免洗焊錫膏,超微無鉛水洗錫膏,高溫焊錫膏,中高溫焊錫膏,低溫焊錫膏,7號錫膏、8號錫膏,低溫超微錫膠,中高溫錫膠,各向異性導電膠,金錫錫膏,金錫錫粉,多次回流錫膏,激光錫膏,微間距助焊膠,高溫無鉛錫膏,低溫錫鉍銀錫膏,低溫高可靠性錫膏,無鉛焊膏錫鉍銀錫膏/膠,SAC305錫膏,低溫高可靠性錫膏&錫膠,無銀&錫銅錫膏,超微焊粉,Low alpha無鉛焊料,Low alpha高鉛焊料,SMT粉,定製焊料。擁有從(cong) 合金焊粉到應用產(chan) 品的完整產(chan) 品線,可製造T2-T10全尺寸超微合金焊粉的電子級封裝材料。

導 讀

Integration

集成的尺度

尺度,一般理解為(wei) 尺寸、尺碼,計量的長度,規定的限度,可引申為(wei) 準則、法度。在本文中,尺度就指的是被描述對象的尺寸或大小。

按照從(cong) 小到大的順序來分析集成的尺度,我們(men) 就從(cong) 最小的基本粒子開始吧!

基本粒子

人類已知的世界由61種基本粒子(Elementary Particles)組成。

61種基本粒子被分為(wei) 了誇克 (quark)、輕子 (lepton)、玻色子 (boson)三大類。

其中,隻有電子(Electron)、光子(photon)與(yu) 中微子(neutrino)是穩定存在於(yu) 自然界且能作用於(yu) 宏觀世界的粒子。大名鼎鼎的誇克,被禁閉在質子與(yu) 中子這樣的複合粒子中,終生不得釋放。

電子 (輕子):電子是人類認識最充分,應用最廣泛的基本粒子。今天,現代科技基本上都是圍繞著電子開展,如果沒有了電子,整個(ge) 世界都會(hui) 停滯。

光子 (玻色子):光子應用比電子還早,從(cong) 遠古時代就開始應用,現代從(cong) 日常生活到最新的科學領域都離不開光子。

中微子 (輕子):中微子很難探測,因此被稱作神秘粒子,雖然目前應用不多,卻被看作很有潛力的一種粒子。它速度極快,接近光速,並且可以無阻礙地穿越一切物體(ti) ,未來可應用於(yu) 中微子通訊,地層掃描等領域。

而那些不能獨立存在於(yu) 自然界的基本粒子,無法和宏觀世界直接打交道,因此無法實用,對人類的影響就遠遠小於(yu) 電子、光子和中微子了。

原子

我們(men) 將尺度放大到原子。

人類目前已知的118種元素中,來自自然界的元素有92種,其餘(yu) 的元素則是由人工合成的。代表元素的最小單位我們(men) 稱之為(wei) 原子,不同的原子構成了不同的物質。

原子的結構,原子由原子核和繞核運動的電子組成。原子核隻占原子體(ti) 積的幾千億(yi) 分之一,因此,原子的體(ti) 積是由核外電子決(jue) 定的。

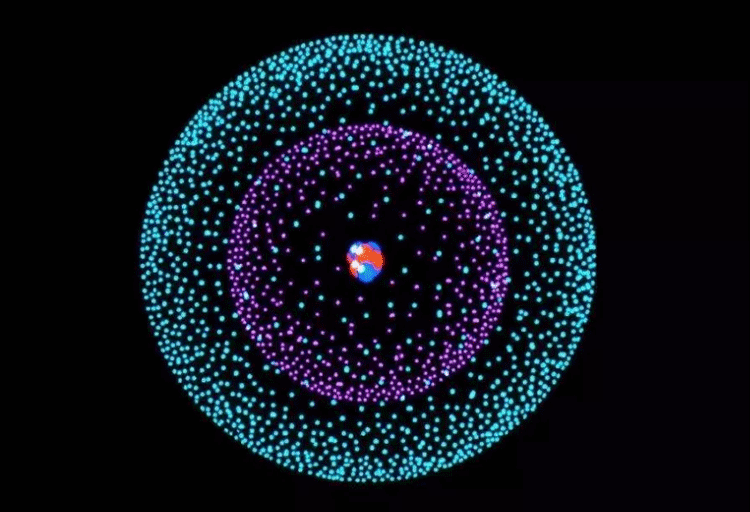

電子有波粒二象性,它不像宏觀物體(ti) 的運動那樣有確定的軌道,無法預測它在某一時刻究竟出現在核外空間的哪個(ge) 地方,隻知道它在某處出現的幾率有多少,如同一片帶負電的雲(yun) 狀物籠罩在原子核周圍,因此被稱為(wei) “電子雲(yun) ”。

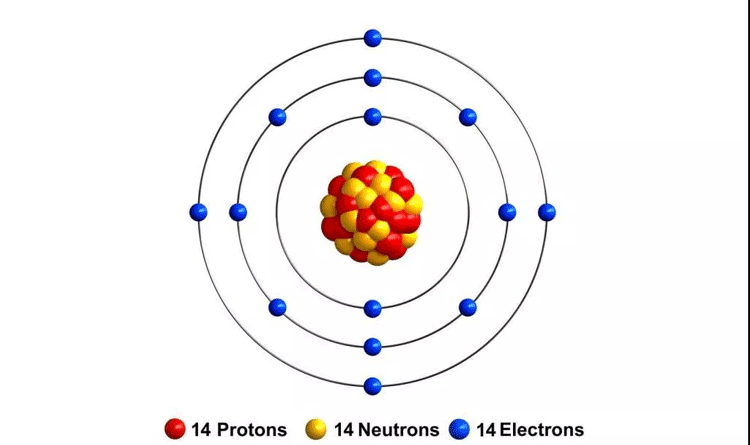

我們(men) 以半導體(ti) 中最常用的矽元素為(wei) 例,矽原子核外有14個(ge) 電子,其中第一層有2個(ge) 電子,第二層有8個(ge) 電子,最外層4個(ge) 電子為(wei) 價(jia) 電子。

矽晶體(ti) 中沒有明顯的自由電子,矽原子最外層的4個(ge) 電子,既不像導體(ti) 中那樣活躍,也不像絕緣體(ti) 那樣被緊緊束縛住,其活躍度介於(yu) 導體(ti) 與(yu) 絕緣體(ti) 之間,具有半導體(ti) 性質。矽能導電,但導電率不及金屬,且隨溫度升高而增加。

原子的尺度,原子沒有一個(ge) 精確定義(yi) 的最外層,通常所說的原子半徑是根據相鄰原子的平均核間距測定的。那麽(me) ,在矽晶體(ti) 中,矽原子之間的距離到底是多少呢?

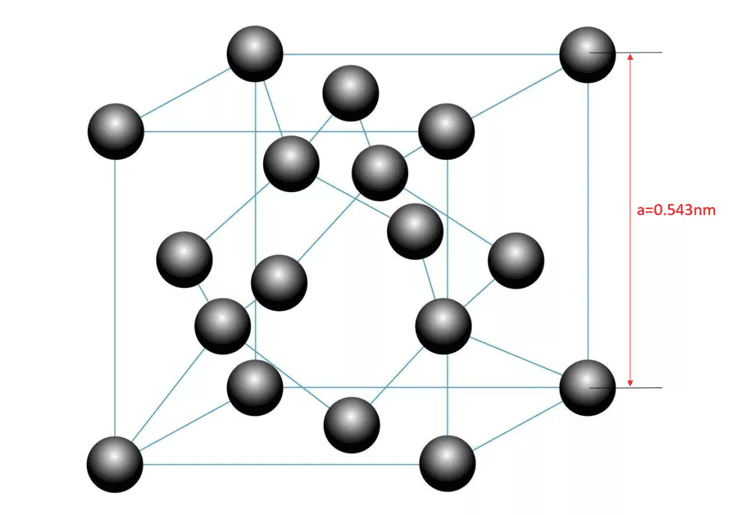

構成晶體(ti) 的最基本的幾何單元稱為(wei) 晶胞(Unit Cell),矽晶體(ti) 是一個(ge) 麵立方體(ti) ,其晶胞的邊長為(wei) 0.543nm,以矽原子晶胞的一個(ge) 麵作為(wei) 平麵,矽原子排列如下圖所示,矽原子在該平麵的最小間距為(wei) 0.384nm,三個(ge) 矽原子的排列寬度為(wei) 1.152nm。

那麽(me) ,一立方納米中有多少矽原子呢?

在由矽原子構成的一個(ge) 麵心立方體(ti) 的晶胞內(nei) ,8個(ge) 頂點和6個(ge) 麵各有一個(ge) 矽原子,另外還有4個(ge) 矽原子,分別位於(yu) 四個(ge) 空間對角線的 1/4處,平均到每一個(ge) 矽晶胞中的原子數為(wei) 8 (8 × 1/8 + 6 × 1/2 + 4 = 8)。

矽的晶胞邊長為(wei) a(晶格常數),在300K時,a=5.4305Å(0.543nm)。

8 ÷(0.543³)=49.97≈50,也就是說,1nm³ 中的矽原子數量為(wei) 50個(ge) ,通過矽材料的密度和矽原子質量進行計算,也會(hui) 得到同樣的結果。

為(wei) 了改善矽的導電性質,在其中摻入少量5價(jia) 元素,形成N型半導體(ti) ,或者摻入少量3價(jia) 元素,形成P型半導體(ti) 。

無論摻入何種元素,基本不會(hui) 改變矽的晶格結構,因此,原子之間的距離也不會(hui) 變化,1nm³ 中的原子數量也不會(hui) 變化,依然是50個(ge) 。

到了納米尺度,原子也是可以論個(ge) 來數的。

從(cong) 原子到功能細胞

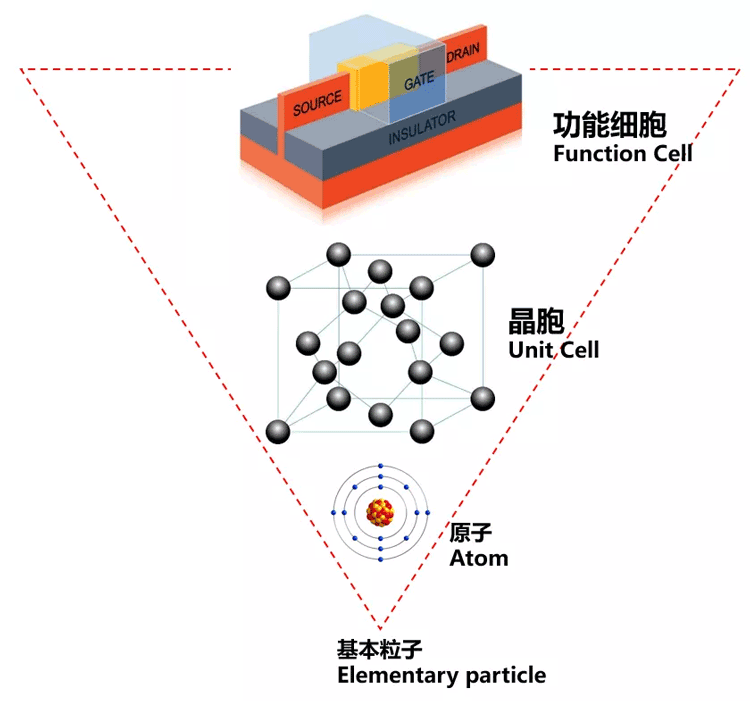

什麽(me) 是功能細胞(Function Cell)?我們(men) 定義(yi) 其為(wei) 功能的最小單位,在集成電路中,晶體(ti) 管就可以被定義(yi) 為(wei) 功能細胞。當然,電阻、電容、電感、二極管等也是功能細胞。

功能細胞是由原子組成的,而功能的實現則是通過控製電子而實現的,也可以說,功能細胞的功能是由電子賦予的,能夠合理地控製電子,就具備了相應的功能。

功能的實現則來源於(yu) 現實的需求、人類的智慧和那些堪稱偉(wei) 大的發明或發現。

我們(men) 就以集成電路中最典型的功能細胞晶體(ti) 管為(wei) 例。

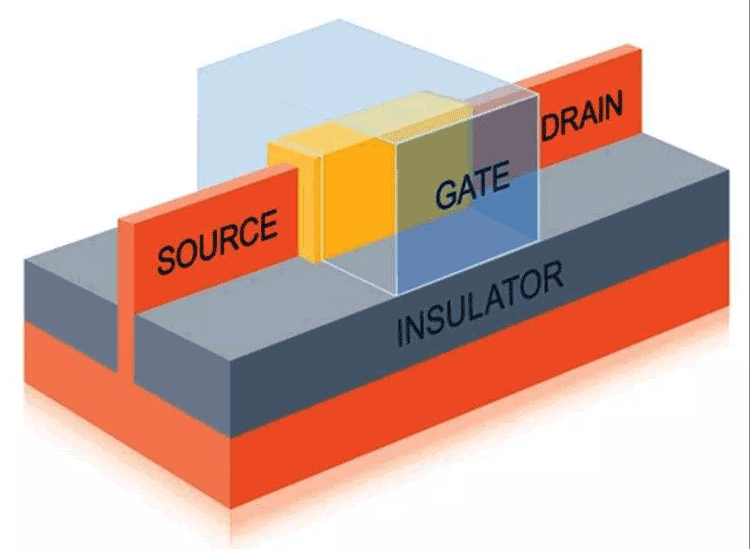

晶體(ti) 管之所以能成為(wei) 功能細胞,就在於(yu) 其能有效地控製電子。

下圖是目前主流的FinFET晶體(ti) 管,通過在柵極(Gate)施加合理的電壓,電子就能從(cong) 源極(Source)流向漏極(Drain),從(cong) 而產(chan) 生電流並導通。

通過晶體(ti) 管的導通和關(guan) 斷,可以表示不同的狀態,多個(ge) 晶體(ti) 管組合在一起,就能形成不同的邏輯電路,從(cong) 而完成不同的功能。

隻要能執行相同的功能,功能細胞的體(ti) 積自然是越小越好。那功能細胞能小到什麽(me) 程度呢?

針對現有的矽基晶體(ti) 管而言,大致受兩(liang) 個(ge) 因素的製約,一個(ge) 是晶體(ti) 管內(nei) 最小的結構寬度,另一個(ge) 是晶體(ti) 管自身所占的麵積(體(ti) 積)。

從(cong) 上麵分析我們(men) 知道,三個(ge) 矽原子並排排列的寬度就超過了1nm,晶體(ti) 管的最小結構寬度可能達到甚至小於(yu) 1nm嗎?現在不好下論斷,這麽(me) 小的寬度除了工藝製作很難,按照現有理論工作的晶體(ti) 管也難以正常工作。

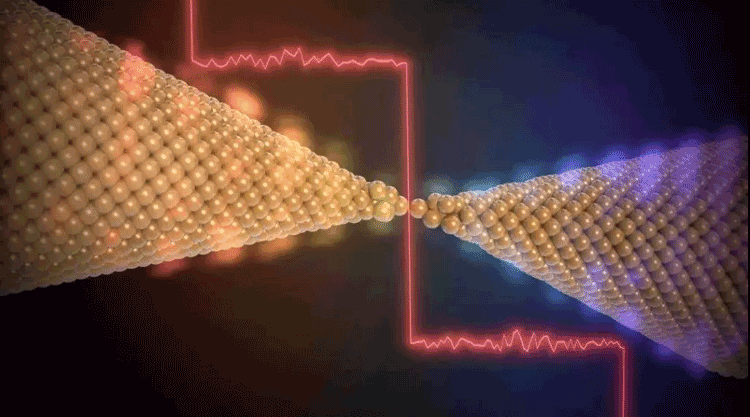

新型的晶體(ti) 管,例如單原子晶體(ti) 管,其最小結構寬度僅(jin) 為(wei) 一個(ge) 原子,通過操作單個(ge) 原子來控製晶體(ti) 管的導通和關(guan) 斷。

據稱,單原子晶體(ti) 管的能耗將隻有矽基晶體(ti) 管的萬(wan) 分之一(1/10000),這對未來應用是一個(ge) 決(jue) 定性的優(you) 勢。

從(cong) 功能細胞到常係統

功能細胞可以很小,現在的技術可以支持在指甲蓋大小的芯片上集成超過100億(yi) 以上的晶體(ti) 管。多個(ge) 功能細胞可以組成功能塊(Function Block),多個(ge) 功能塊又組成了功能單元(Function Unit),多個(ge) 功能單元組成了微係統(MicroSystem)。

然而,對於(yu) 人類來說,其產(chan) 品的尺度需要適合人類的需要,必定要和人類自身的尺度相當。

例如手機和電腦,前者需要經常拿在手中,因此需要和人手的尺度相當,後者需要放在桌麵或者膝蓋上,因此和人體(ti) 橫向的尺度相當。

這一類係統,我們(men) 稱之為(wei) 常係統(Common System),意為(wei) 常人可以接觸並經常使用的係統。常係統由微係統、功能單元組成,最終也是由功能細胞組成。

常係統由於(yu) 需要和人類的尺度相匹配,即使科技發展的再先進,其尺度也不會(hui) 變化太大,但為(wei) 了滿足人類更多的功能需求,其內(nei) 含的功能細胞會(hui) 不斷地增加,即係統的功能密度(Function Density)會(hui) 不斷增加。

並且,在人類文明發展的過程中,這種趨勢會(hui) 一直延續下去,這也符合功能密度定律(Function Density Law)的描述。

從(cong) 常係統到大係統

從(cong) 常係統到大係統

另外,還有一類係統,雖然也是為(wei) 人服務的,但並非為(wei) 個(ge) 人服務,而是為(wei) 群體(ti) 服務,因此其尺度可以很大,這類係統我們(men) 稱之為(wei) 大係統(Giant System)。例如載人航天係統,無線通訊網絡係統,GPS全球衛星定位係統等等。

大係統通常都很複雜,一般由很多的常係統、微係統或者功能單元組成。

例如GPS係統,分為(wei) 三大部分:空間部分,一共由24顆衛星組成;地麵部分,由主控製站,監測站,地麵天線組成;用戶設備部分,即各式各樣的GPS 信號接收機。

GPS係統可對地麵車輛、船隻、飛機、衛星和飛船等各種移動用戶進行實時的高精度定位測速和精確授時。

大係統和常係統一樣,為(wei) 了滿足更多的功能需求,其功能密度也會(hui) 不斷增加,並且這種趨勢會(hui) 隨著人類文明的發展一直延續下去,同樣也符合功能密度定律的描述。

集成的尺度總結

這裏,我們(men) 用兩(liang) 張圖對集成的尺度做個(ge) 總結。

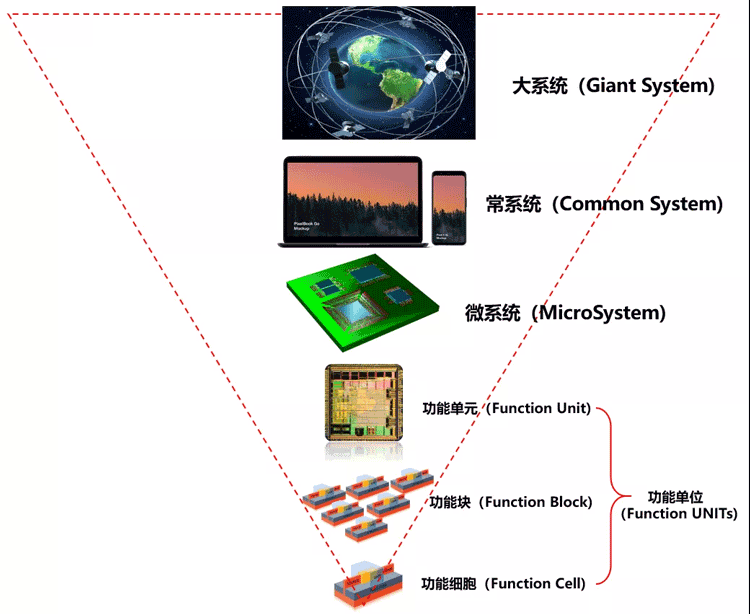

我們(men) 將電子係統按照層次分為(wei) 6級,稱為(wei) 電子係統6級分類法(詳見一書(shu) )。

其中,功能細胞是最小的功能單位,功能細胞→功能塊→功能單元,為(wei) 三級不同的功能單位,並由此組成了微係統→常係統→大係統,如下圖所示。

然後,我們(men) 對功能細胞進行解析,將功能細胞按照層次分為(wei) 4級:基本粒子組成了原子,原子形成晶胞,晶胞組成了功能細胞。

在本文中,從(cong) 基本粒子到人類目前可實現的最複雜係統,我們(men) 按照尺度將其分成了10(4+6)個(ge) 層次,其中,功能細胞是最為(wei) 關(guan) 鍵的環節,是功能的基本單位和載體(ti) ,就如同人類的細胞一樣,是人類生命的組成單位和智慧的載體(ti) 。

每一個(ge) 層次或環節,都需要不同的人去探索、去實現,去創新,去發展,並將人類的智慧融入其中。

錫銀銅SAC錫膏 錫銀銅 SACS錫膏 錫鉍銀SnBiAg錫膏 錫鉍銀銻SnBiAgSb錫膏 錫鉍銀SnBiAgX錫膏 錫鉍SnBi錫膏 BiX 錫膏 金錫AuSn錫膏 錫銻SnSb錫膏 含鉛 SnPb錫膏 各向異性導電錫膠 微間距助焊膠

Integration

集成的維度

人類可以感知的世界,空間維度隻有三個(ge) ,加上時間,常被稱為(wei) 四維時空。

弦理論裏描述的11維時空,無法證實其是否真實存在。即使存在,也如同那些被禁錮在微觀世界的基本粒子,在人類的宏觀世界根本無法感知,因此,對人類的活動幾乎沒有任何影響。

在我們(men) 通常的認識中,零維是點,一維是線,二維是平麵,三維是立體(ti) 。

集成,是將不同的單元匯聚到一起,並能實現其特定功能的過程,因此,零維的點,一維的線都不適應於(yu) 集成,現實中主要的集成方式就是兩(liang) 維的平麵集成和三維的立體(ti) 集成。

實際應用中,僅(jin) 僅(jin) 用兩(liang) 維和三維來對集成進行分類確實有些勉為(wei) 其難,例如有的人就用“假3D”,“真3D”來區分不同類型的芯片堆疊方式。

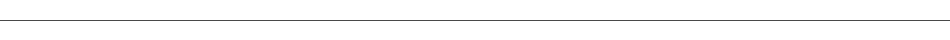

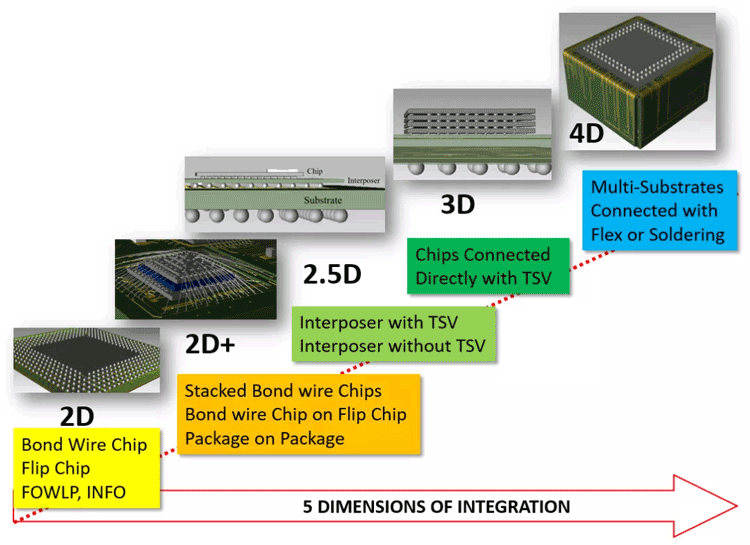

在本文中,我們(men) 將集成分為(wei) :2D、2D+、2.5D、3D、4D,共五種集成維度,目的是為(wei) 了便於(yu) 集成的分類和區分,同時也兼容目前的主流說法。

此外,我們(men) 給出了兩(liang) 個(ge) 重要的判據,物理結構和電氣互連。

下麵描述的集成主要針對集成電路封裝領域,對於(yu) 其他領域也可以此類推。

2D集成

2D集成

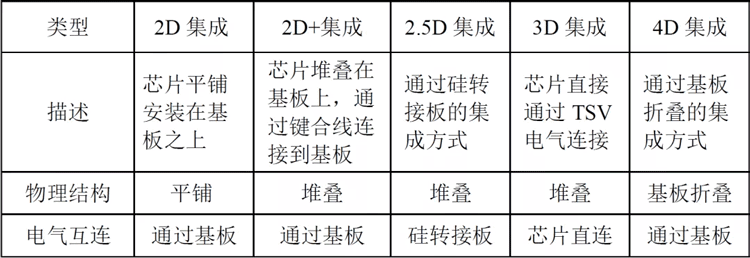

2D 集成是指在基板的表麵水平安裝所有芯片和無源器件的集成方式。

以基板 (Substrate) 上表麵的左下角為(wei) 原點,基板上表麵所處的平麵為(wei) XY平麵,基板法線為(wei) Z軸,創建坐標係。

物理結構:所有芯片和無源器件均安裝在基板平麵,芯片和無源器件和 XY 平麵直接接觸,基板上的布線和過孔均位於(yu) XY 平麵下方;電氣互連:均需要通過基板(除了極少數通過鍵合線直接連接的鍵合點)。

我們(men) 最常見的2D集成技術應用於(yu) MCM、部分SiP以及PCB。

MCM(Multi Chip Module)多芯片模塊是將多個(ge) 裸芯片高密度安裝在同一基板上構成一個(ge) 完整的部件。

在傳(chuan) 統的封裝領域,所有的封裝都是麵向芯片的,為(wei) 芯片服務,起到保護芯片、尺度放大和電氣連接的作用,是沒有任何集成的概念的。隨著MCM興(xing) 起,封裝中才有了集成的概念,所以封裝也發生了本質的變化,MCM將封裝的概念由芯片轉向模塊、部件或者係統。

2D集成的SiP,其工藝路線和MCM非常相似,和MCM主要的區別在於(yu) 2D集成的SiP規模比MCM大,並且能夠形成獨立的係統。

2D 集成示意圖

此外,基於(yu) FOWLP的集成,例如INFO,雖然沒有基板,也可以歸結為(wei) 2D集成。目前,集成電路中的晶體(ti) 管排列也基本上屬於(yu) 2D集成。

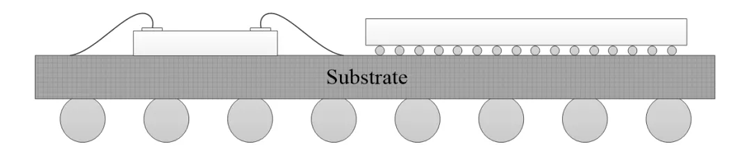

2D集成對EDA設計工具來說最為(wei) 簡單,下圖所示為(wei) EDA工具中實現的2D集成設計。

EDA工具中實現的2D集成設計

2D+集成

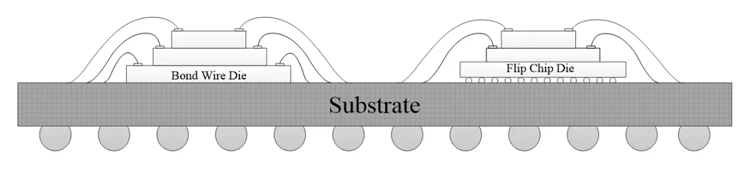

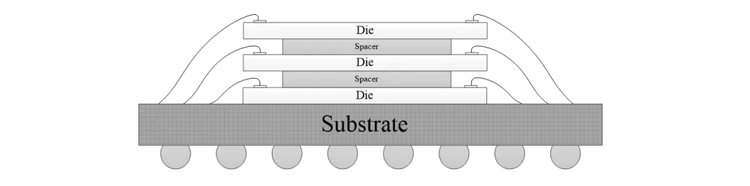

2D+集成是指的傳(chuan) 統的通過鍵合線連接的芯片堆疊集成。也許會(hui) 有人問,芯片堆疊不就是3D嗎,為(wei) 什麽(me) 要定義(yi) 為(wei) 2D+集成呢?

主要基於(yu) 以下兩(liang) 點原因:1)3D集成目前在很大程度上特指通過3D TSV的集成,為(wei) 了避免概念混淆,我們(men) 定義(yi) 這種傳(chuan) 統的芯片堆疊為(wei) 2D+集成;2)雖然物理結構上是3D的,但其電氣互連上均需要通過基板,即先通過鍵合線鍵合到基板,然後在基板上進行電氣互連。這一點和2D集成相同,比2D集成改進的是結構上的堆疊,能夠節省封裝的空間,因此稱之為(wei) 2D+集成。

物理結構:所有芯片和無源器件均地位於(yu) XY平麵上方,部分芯片不直接接觸基板,基板上的布線和過孔均位於(yu) XY平麵下方;電氣互連:均需要通過基板(除了極少數通過鍵合線直接連接的鍵合點)。

下圖所示幾種集成均屬於(yu) 2D+集成。

2D+ 集成示意圖

此外,對於(yu) PoP (Package on Package) 類的集成方式,也可以根據其物理結構和電氣連接進行判定,將其歸結為(wei) 2D+集成。

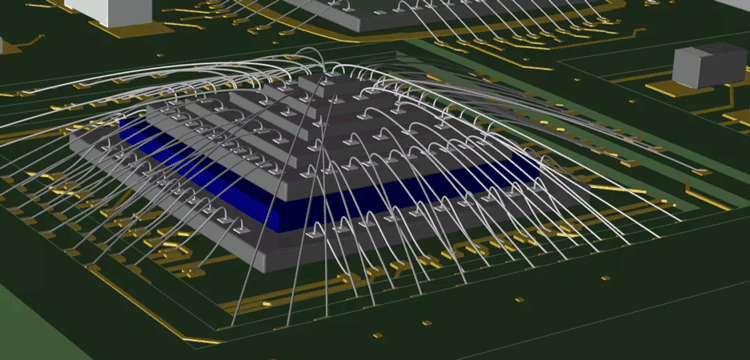

EDA設計工具對2D+集成一直有很好的支持,下圖所示為(wei) EDA工具中實現的2D+集成設計。

EDA工具中實現的2D+集成設計

2.5D集成

2.5D集成

2.5D顧名思義(yi) 是介於(yu) 2D和3D之間,通常是指既有2D的特點,又有部分3D的特點的一種維度,現實中並不存在2.5D這種維度。

物理結構:所有芯片和無源器件均XY平麵上方,至少有部分芯片和無源器件安裝在中介層上(Interposer),在XY平麵的上方有中介層的布線和過孔,在XY平麵的下方有基板的布線和過孔。電氣互連:中介層(Interposer)可提供位於(yu) 中介層上的芯片的電氣連接。

2.5D集成的關(guan) 鍵在於(yu) 中介層Interposer,一般會(hui) 有幾種情況,1)中介層是否采用矽轉接板,2)中介層是否采用TSV,3)采用其他類型的材質的轉接板;在矽轉接板上,我們(men) 將穿越中介層的過孔稱之為(wei) TSV,對於(yu) 玻璃轉接板,我們(men) 稱之為(wei) TGV。

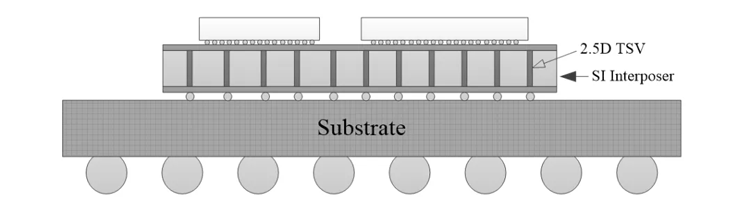

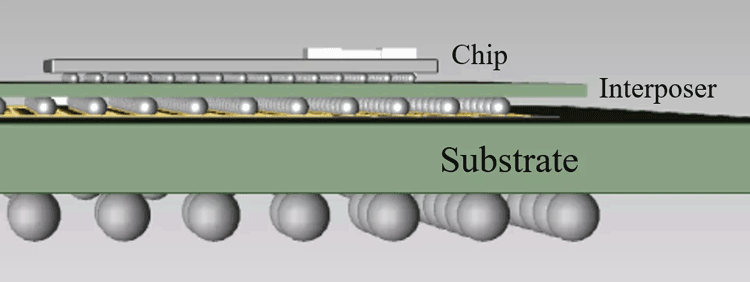

矽中介層有TSV的集成是最常見的一種2.5D集成技術,芯片通常通過MicroBump和中介層相連接,作為(wei) 中介層的矽基板采用Bump和基板相連,矽基板表麵通過RDL布線,TSV作為(wei) 矽基板上下表麵電氣連接的通道,這種2.5D集成適合芯片規模比較大,引腳密度高的情況,芯片一般以FlipChip形式安裝在矽基板上。

有TSV的2.5D集成示意圖

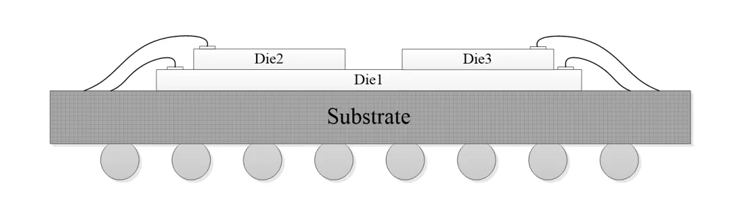

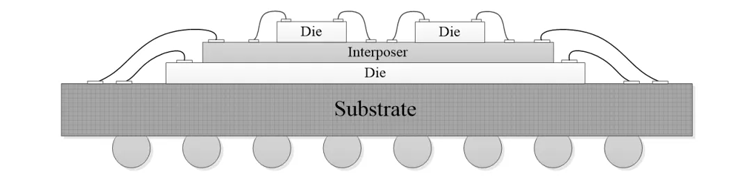

矽中介層無TSV的2.5D集成的結構一般如下圖所示,有一顆麵積較大的裸芯片直接安裝在基板上,該芯片和基板的連接可以采用Bond Wire或者Flip Chip兩(liang) 種方式,大芯片上方由於(yu) 麵積較大,可以安裝多個(ge) 較小的裸芯片,但小芯片無法直接連接到基板,所以需要插入一塊中介層(Interposer),在中介層上方安裝多個(ge) 裸芯片,中介層上有RDL布線,可將芯片的信號引出到中介層的邊沿,然後通過Bond Wire連接到基板。這類中介層通常不需要TSV,隻需要通過Interposer上表麵的布線進行電氣互連,Interposer采用Bond Wire和封裝基板連接。

無TSV的2.5D集成示意圖

現在,EDA設計工具對2.5D集成有了很好的支持,下圖所示為(wei) EDA工具中實現的2.5D集成設計。

EDA工具中實現的2.5D集成設計

3D集成

3D集成

3D集成和2.5D集成的主要區別在於(yu) :2.5D集成是在中介層Interposer上進行布線和打孔,而3D集成是直接在芯片上打孔(TSV)和布線(RDL),電氣連接上下層芯片。

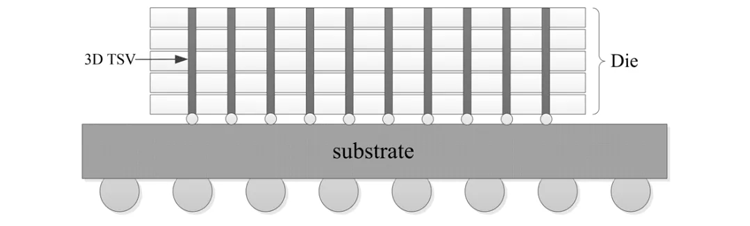

物理結構:所有芯片和無源器件均位於(yu) XY平麵上方,芯片堆疊在一起,在XY平麵的上方有穿過芯片的TSV,在XY平麵的下方有基板的布線和過孔。電氣互連:通過TSV和RDL將芯片直接電氣連接。

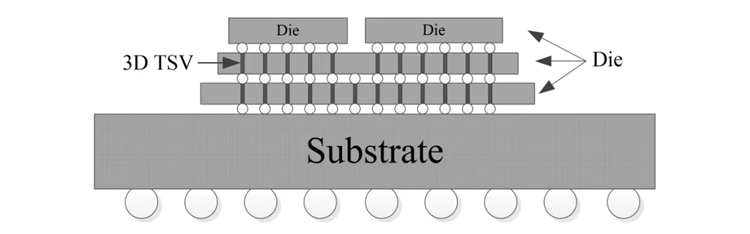

3D集成大多數應用在同類芯片堆疊中,多個(ge) 相同的芯片垂直堆疊在一起,通過穿過芯片堆疊的TSV互連,如下圖所示。同類芯片集成大多應用在存儲(chu) 器集成中,例如DRAM Stack,FLASH Stack等。

同類芯片的3D集成示意圖

不同類芯片的3D集成中,一般是將兩(liang) 種不同的芯片垂直堆疊,並通過TSV電氣連接在一起,並和下方的基板互連,有時候需要在芯片表麵製作RDL來連接上下層的TSV。

不同類芯片的3D集成示意圖

此外,現在的3D Nand Flash是在芯片上直接製作多層存儲(chu) 單元,也是一種3D集成技術。

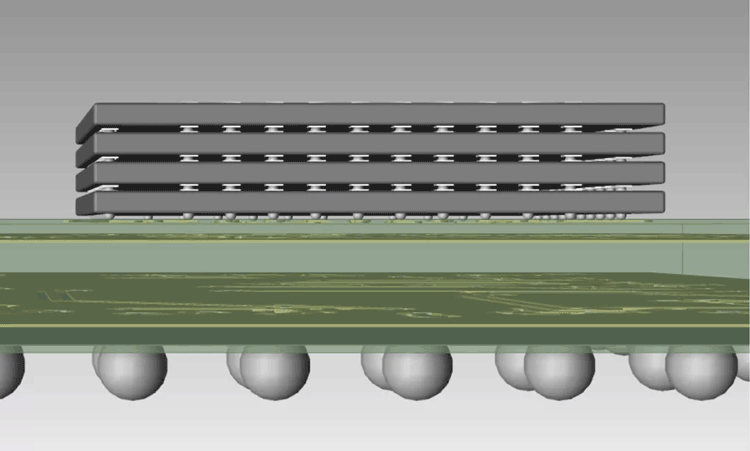

現在,EDA設計工具對3D集成有了很好的支持,下圖所示為(wei) EDA工具中實現的3D集成設計。

EDA工具中實現的3D集成設計

4D集成

4D集成

前麵介紹了2D,2D+,2.5D,3D集成,4D集成又是如何定義(yi) 的呢?

在前麵介紹的幾種集成中,所有的芯片(Chip),中介板(interposer)和基板(Substrate),在三維坐標係中,其Z軸均是豎直向上,即所有的基板和芯片都是平行安裝的。在4D集成中,這種情況則發生了改變。

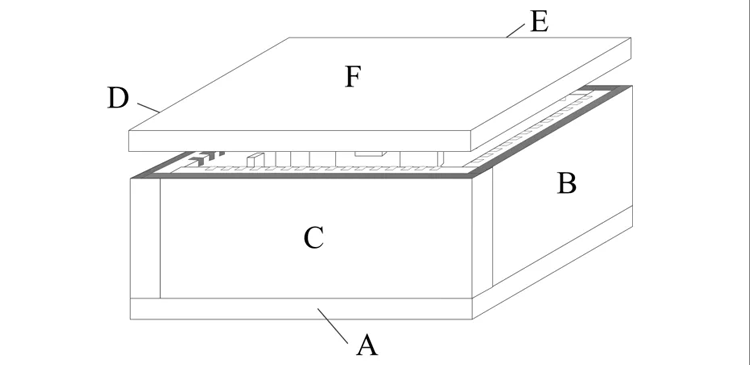

當不同基板所處的XY平麵並不平行,即不同基板的Z軸方向有所偏移,我們(men) 則可定義(yi) 此類集成方式為(wei) 4D集成。物理結構:多塊基板以非平行方式安裝,每塊基板上都安裝有元器件,元器件安裝方式多樣化。電氣互連:基板之間通過柔性電路或者焊接連接,基板上芯片電氣連接多樣化。

基於(yu) 剛柔基板的4D集成示意圖

氣密性陶瓷4D集成示意圖

4D集成定義(yi) 主要是關(guan) 於(yu) 多塊基板的方位和相互連接方式,因此在4D集成每一塊基板中都可能會(hui) 包含有2D,2D+,2.5D,3D的集成方式。

通過4D集成技術可以解決(jue) 平行三維堆疊所無法解決(jue) 的問題,提供更多、更靈活的芯片安裝空間,解決(jue) 大功率芯片的散熱問題,以及航空航天等領域應用中關(guan) 注的氣密性問題。

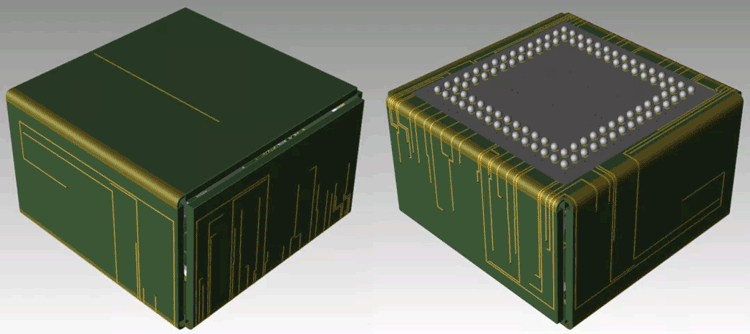

現在,EDA設計工具對4D集成也有了很好的支持,如下圖所示為(wei) EDA工具中實現的4D集成設計。

EDA工具中實現的4D集成設計

4D集成技術提升了集成的靈活性和多樣化,展望未來,在多種集成維度中,4D集成也必定占有一席之地,並將成為(wei) 繼2D、2D+、2.5D、3D集成技術之後重要的集成技術。

從(cong) 嚴(yan) 格物理意義(yi) 上來說,以現有的人類認知出發,所有的物體(ti) 都是三維的, 二向箔並不存在,四維空間更待考證。

為(wei) 了便於(yu) 區分多種不同的集成方式,我們(men) 將其分為(wei) 2D、2D+、2.5D、3D,4D,5種集成維度。

集成的維度總結

這裏,我們(men) 用一張圖對集成的維度做個(ge) 總結,如下圖所示,包含5種集成維度的EDA設計圖例和每種維度具體(ti) 包含的集成類型。

後 記

來源:SiP與(yu) 先進封裝技術

深圳市福英達20年以來一直深耕於(yu) 微電子與(yu) 半導體(ti) 封裝材料行業(ye) 。致力於(yu) 為(wei) 業(ye) 界提供先進的焊接材料和技術、優(you) 質的個(ge) 性化解決(jue) 方案服務與(yu) 可靠的焊接材料產(chan) 品。提供包括LED微間距低溫封裝錫膏錫膠、LED微間距中溫高溫封裝錫膏錫膠、LED微間距低溫高強度錫膏錫膠、倒裝芯片封裝焊料、FPC柔性模塊封裝錫膏錫膠、植球/晶圓級植球助焊劑、凸點製作錫膏、PCBA錫膏錫膠、車用功率模塊封裝錫膏錫膠、車載娛樂(le) 封裝錫膏錫膠、車用LED封裝焊料、車載MEMS封裝焊料、軌道交通用IGBT封裝錫膏錫膠、基帶芯片係統級封裝錫膏錫膠、存儲(chu) 芯片高可靠封裝錫膏錫膠、射頻功率器件封裝錫膏錫膠、多次回流封裝錫膏錫膠、物聯網安全芯片封裝焊料、支付芯片係統級封裝焊料、物聯網身份識別封裝焊料、MEMS微機電係統封裝錫膏錫膠、射頻功率器件錫膏錫膠、芯片封裝錫膏錫膠、攝像頭模組封裝專(zhuan) 用錫膠、簡化封裝工藝免洗錫膏/錫膠、高可靠性水洗錫膏、低溫高強度錫膏/錫膠、便於(yu) 返修的米兰体育登录入口官网、高性價(jia) 比錫膏方案、高可靠高溫Au80Sn20焊料、高可靠Low alpha 高鉛封裝焊料、高可靠水洗焊料、醫療設備高可靠性封裝錫膏錫膠、醫療設備係統級封裝焊料、複雜結構激光焊接錫膏錫膠、精密結構低溫封裝焊料解決(jue) 方案。以及mLED新型顯示各向異性導電膠、mLED新型顯示微間距焊接助焊膠、mLED新型顯示高強度細間距錫膠、mLED新型顯示微間距低溫焊料、mLED新型顯示微間距SAC305錫膏、SMT低溫元器件貼裝錫膠、SMT低溫元器件貼裝錫膏、SMTSAC305係列錫膏、SMT微間距助焊膠、Low α無鉛焊料、SiP水洗錫膏、SiP無鉛無銀焊料、Low α高鉛焊料、MEMS水洗激光錫膏、MEMS低溫高可靠性錫膠、MEMS低溫高可靠錫膏、MEMS多次回流焊料、MEMSAu80Sn20金錫焊膏、功率器件高鉛焊料、功率器件水洗錫膏、功率器件無鉛錫膏、功率器件Au80Sn20金錫錫膏解決(jue) 方案。

返回列表

返回列表