通過表麵處理實現高可靠性無鉛焊點

通過表麵處理實現高可靠性無鉛焊點

福英達——研發中心——羅樹全

摘要

隨著半導體(ti) 技術的不斷更新發展,電子封裝的小型化、高速化、高可靠性要求的提高,對電子封裝過程中的精細化工藝提出了更高的要求,從(cong) 而使達到封裝的要求。這裏我們(men) 說到的電子封裝基材表麵處理是說對不同焊接基板進行物理或化學處理的方法,從(cong) 而達到焊接焊點的可靠性。

化學鍍是不使用加電流的方式,僅(jin) 靠鍍液中的還原劑進行氧化還原反應,在金屬表麵的催化作用下使金屬離子不斷沉積於(yu) 金屬表麵的過程。由於(yu) 化學鍍必須在具有自催化性的材料表麵專(zhuan) 題進行,因而化學鍍又稱“自催化鍍”。常見的化學鍍有鍍鎳、鍍金、鍍銅、鍍鈷等。經過不同的化學鍍層,使其焊接基板上形成一層保護鍍層,在焊接過程中起到正麵的作用,從(cong) 而實現高可靠性焊點的連接,在電子封裝領域得到廣泛的應用。

一、關(guan) 於(yu) 浸錫的問題

1.1鍍錫過程需要更長的時間

鍍錫就是把需要焊接基板,放進金屬鹽溶液中,在化學置換原理下使其焊接基板沉積出金屬層,以此到達所需的焊接效果。

浸錫過程中由於(yu) 工藝複雜一般需要時間10~15分鍾;而使用OSP工藝的話就大大縮減,一般需要1分鍾;浸銀工藝過程時間也比較短,一般需要0.5~3分鍾。

1.2銅在鍍錫過程中的積累,鍍錫層厚度和成本的分析

在浸錫過程中,使用硫脲化學試劑使Sn2+被Cu2+取代,每個(ge) 錫原子的沉澱就會(hui) 有兩(liang) 個(ge) Cu2+形成,因此錫將取代銅。而在浸銀過程中,每個(ge) 錫原子的沉澱就會(hui) 有半個(ge) Cu2+形成。在浸錫和浸銀的過程中都避免不了有銅的積累。

在鍍錫過程中,為(wei) 了使焊後接焊點可靠性更加穩定,我們(men) 通常將鍍錫的厚度控製在1~1.2微米左右,是鍍銀厚度的5~6倍。

在成本方麵,浸錫工藝的成本是0.5美元/平方米;而OSP工藝的成本要大大的降低是0.15美元/平方米;浸銀工藝則是0.15~0.25美元/平方米。

二、關(guan) 於(yu) 鎳沉金的問題

2.1鎳沉金的優(you) 點和造成黑盤的原因

鎳沉金工藝就是在銅的焊接基板上經過化學反應置換出鈀,再在鈀核上化學鍍上一層鎳磷合金層,然後通過置換反應在鎳上鍍一層金。鎳沉金表麵處理具有平整度高、接觸電阻低、耐磨性、耐熱性好及貯存時間長等優(you) 點,且其兼具可焊接、可觸通、可打線與(yu) 可散熱四種功能於(yu) 一身,一向廣泛應用於(yu) 各種密集組裝板類,具有其它表麵處理所無法取代的地位。金屬離子沉澱不需要經過電氣連接,能耗上比電鍍更有優(you) 勢。

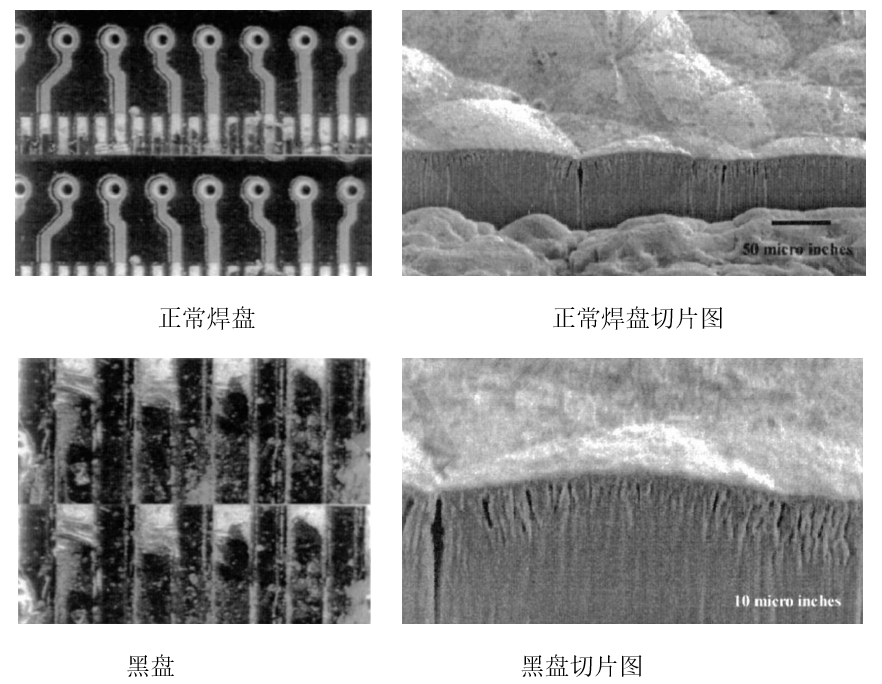

在浸金工藝過程中如果我們(men) 處理不當,就會(hui) 造成基板腐蝕,使其浸金的過程造成了黑盤現象,下麵圖像可以看出腐蝕進一步改變了表麵的結構[1],

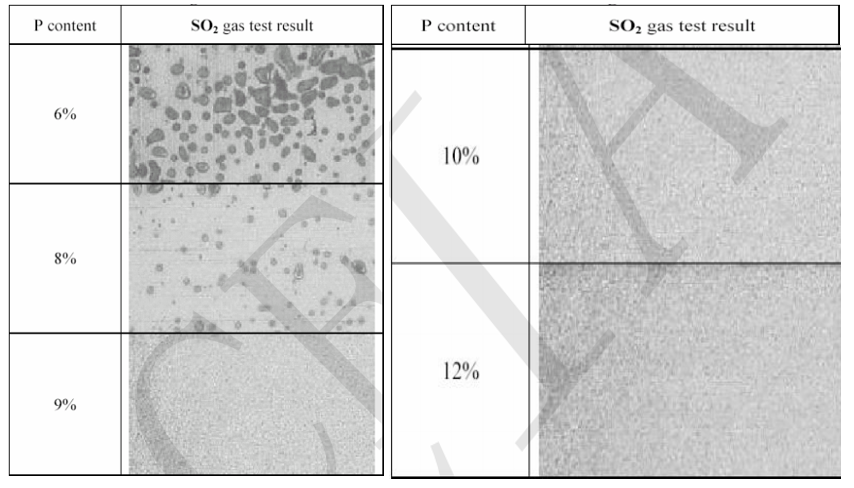

2.2在鎳層中加入磷可以提高焊盤的耐腐蝕性,對焊點可靠性增加

經過大量數據和實驗證明在鎳盤中加入磷會(hui) 增加焊盤的耐腐性,使得焊點可靠性得以加強。下圖是加入不同含量磷的鎳盤在通二氧化硫氣體(ti) 下的腐蝕程度[2]

從(cong) 上圖可以得出,在鎳層中加入9%及以上的磷含量焊盤的耐腐蝕性效果最佳

三、關(guan) 於(yu) 浸銀的問題

3.1在IMC(0.25mil)的橫截麵高低都存在很多微小的空洞

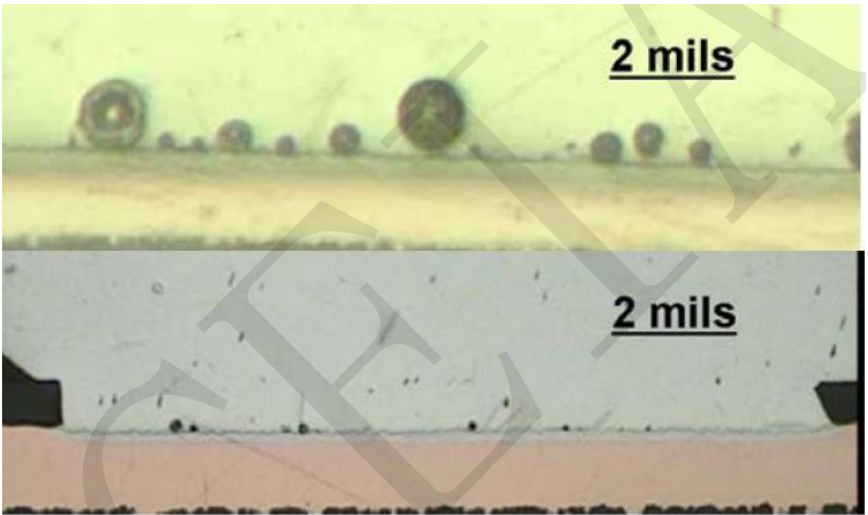

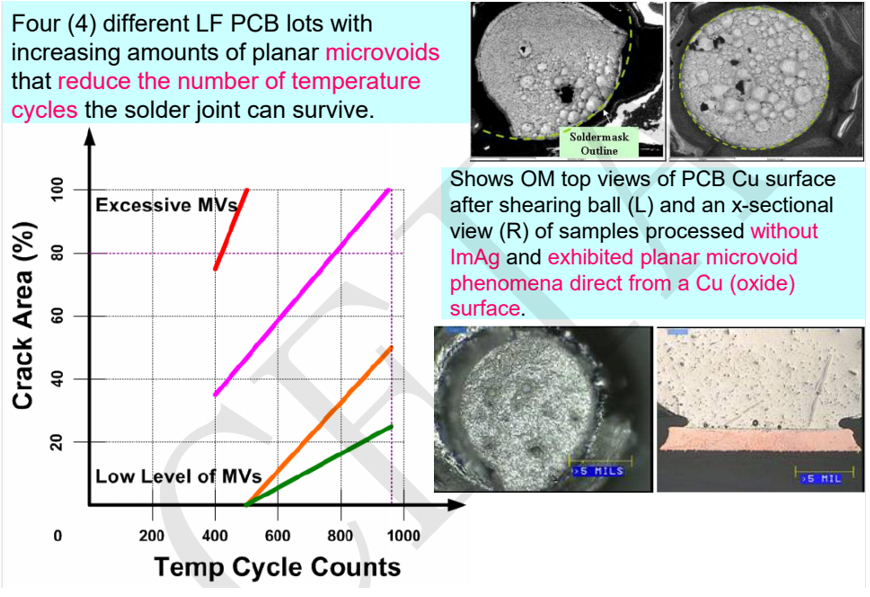

我們(men) 在焊接過程中效果不佳時,使得焊點的IMC層的可靠性出現問題,產(chan) 生許多空洞,如圖所示[3],

我們(men) 在焊接時基板的銅會(hui) 受到不同程度的腐蝕,從(cong) 而產(chan) 生銅坑,在焊點裏麵產(chan) 生空洞現象,如下圖所示[4]

四、總結

焊接基材的表麵處理最基本的目的是保證良好的可焊性或電性能,使其在焊接過程中形成的焊點可靠性加強。我們(men) 焊接所用的基材大部分是銅成分,由於(yu) 自然界的銅在空氣中傾(qing) 向於(yu) 以氧化物的形式存在,不大可能長期保持為(wei) 原銅,因此需要對銅進行其他處理。在後續的組裝中,可以采用強助焊劑除去大多數銅的氧化物。強助焊劑因其不易去除,所以很少采用。采用浸錫,浸銀,化鎳金等表麵處理工藝,能夠有效的保證良好的可焊性,電性能以及焊點可靠性,在半導體(ti) 封裝領域得到廣泛的應用。

福英達專(zhuan) 注於(yu) 微電子與(yu) 半導體(ti) 封裝焊料領域20餘(yu) 年,福英達工業(ye) 科技有限公司是一家全球領先的微電子與(yu) 半導體(ti) 封裝材料方案提供商,國家高新技術企業(ye) ,深耕於(yu) 微電子與(yu) 半導體(ti) 封裝材料行業(ye) ,從(cong) 合金焊粉到應用產(chan) 品線完整,是目前全球唯一可製造T2-T10全尺寸超微合金焊粉的電子級封裝材料製造商。米兰app官方正版官网入口錫膏、錫膠及合金焊粉等產(chan) 品廣泛應用於(yu) 微電子與(yu) 半導體(ti) 封裝的各個(ge) 領域。得到全球SMT電子化學品製造商、微光電製造商和半導體(ti) 封裝測試商的普遍認可。但微電子與(yu) 半導體(ti) 封裝材料問題廣泛,在此我們(men) 僅(jin) 就常見問題展開了敘述。因工藝過程不同,其過程中所涉及到的問題也可能不盡相同。歡迎您就具體(ti) 問題與(yu) 我們(men) 的專(zhuan) 業(ye) 人員進行溝通討論。我們(men) 希望同合作夥(huo) 伴共同與(yu) 時俱進,共同探究新問題、新技術以及複雜工藝,努力為(wei) 合作夥(huo) 伴提供專(zhuan) 業(ye) 、周到的微電子與(yu) 半導體(ti) 封裝焊接材料服務。

參考文獻

[1]Zequn Mei, Samuel K. Liem, and Allan Shih, “A Failure Analysis and Rework Method of Electronic Assembly on Electroless Ni / Immersion Au SurfaceFinish”, SMTA, Chicago, IL, 1999.

[2]Masahiro Nozu, Akira Kuzuhara, Atsuko Hayashi, Hiroshi Otake, Shigeo Hashimoto, and Donald Gudeczauskas (C.Uyemura & Co.,Ltd.), “High Phosphorous Electroless Nickel Process for mobiles phones PWBs”, Apex, S10-1-1, Anaheim, CA, Feb, 2004

[3]Muffadal Mukadam, Norman Armendariz*, Raiyo Aspandiar, Mike Witkowski, Victor Alvarez, Andrew Tong, Betty Phillips, and Gary Long (Intel Corporation), " PLANAR MICROVOIDING IN LEAD-FREE SECOND-LEVEL INTERCONNECT SOLDER JOINTS", SMTAI, September, 2006, Chicago, IL

[4]Muffadal Mukadam, Norman Armendariz*, Raiyo Aspandiar, Mike Witkowski, Victor Alvarez, Andrew Tong, Betty Phillips, and Gary

Long (Intel Corporation), " PLANAR MICROVOIDING IN LEAD-FREE SECOND-LEVEL INTERCONNECT SOLDER JOINTS",

SMTAI, September, 2006, Chicago, IL

返回列表

返回列表